Từng là một giải pháp chuyên biệt nhằm tối ưu hóa năng suất sản xuất chip silicon, chiplet giờ đây đã trở thành chiến lược chủ đạo của ngành công nghiệp bán dẫn để cung cấp nhiều nhân xử lý hơn với chi phí thấp hơn. AMD là hãng tiên phong phổ biến cách tiếp cận này với các dòng sản phẩm Ryzen và EPYC, sau đó Intel miễn cưỡng đi theo, và hiện tại ngay cả NVIDIA cùng Qualcomm cũng đang bắt đầu áp dụng. Tuy nhiên, mặc dù chiplet mang lại những lợi ích không thể phủ nhận như phân loại chip tốt hơn (better binning), giảm chi phí tấm bán dẫn (wafer costs) và khả năng mở rộng thiết kế linh hoạt, chúng cũng đi kèm với những thỏa hiệp mà các nhà sản xuất có thể không muốn bạn tìm hiểu sâu.

Từ Thiết Kế Nguyên Khối Đến Kiến Trúc Chiplet: Bước Tiến Đầy Thách Thức

Sản Xuất Tiết Kiệm Hơn, Nhưng Độ Trễ Tăng Cao

Giấc mơ về một con chip nguyên khối duy nhất với độ trễ thấp, băng thông cao và không có chi phí kết nối phức tạp (interconnect overhead) vẫn còn là một điều gì đó xa vời trong các thiết kế bộ xử lý hiện đại. Việc chuyển sang kiến trúc chiplet làm tăng thêm độ phức tạp đáng kể. Mỗi die bổ sung đồng nghĩa với một tập hợp các kết nối liên chip (interconnect) mới. Mặc dù các nhà cung cấp luôn ca ngợi về tốc độ siêu nhanh của các đường kết nối giữa các die, nhưng thực tế là độ trễ tăng lên, các giới hạn về băng thông xuất hiện, và phần mềm cần phải được tối ưu để thích nghi. Ví dụ điển hình là AMD Infinity Fabric, dù đã trưởng thành đáng kể kể từ kiến trúc Zen 2, nhưng vẫn tạo ra những “phí tổn” nhất định so với một thiết kế nguyên khối truyền thống.

Để dễ hình dung, độ trễ trong bối cảnh bộ xử lý và hiệu suất là khoảng thời gian cần thiết để thông tin di chuyển từ điểm A đến điểm B. Thông tin di chuyển càng lâu thì độ trễ càng lớn, đồng nghĩa với việc thông tin đến đích càng chậm. Với các thiết kế bộ xử lý nguyên khối, nơi tất cả các thành phần chính của chip nằm gọn trong một gói duy nhất, thông tin có ít quãng đường phải di chuyển hơn. Điều này về mặt lý thuyết có nghĩa là thông tin đến đích nhanh hơn.

Trong trường hợp các bộ xử lý dựa trên thiết kế chiplet, các kết nối liên chip (interconnect) như AMD Infinity Fabric hoạt động như một “xa lộ” hay “đường cao tốc” đóng vai trò là tuyến đường trực tiếp giữa A và B. Vấn đề là việc thêm một “xa lộ” tạo ra khoảng cách giữa A và B. Khoảng cách càng lớn, thông tin càng phải đi xa hơn, điều này ngụ ý rằng độ trễ sẽ cao hơn một cách tự nhiên.

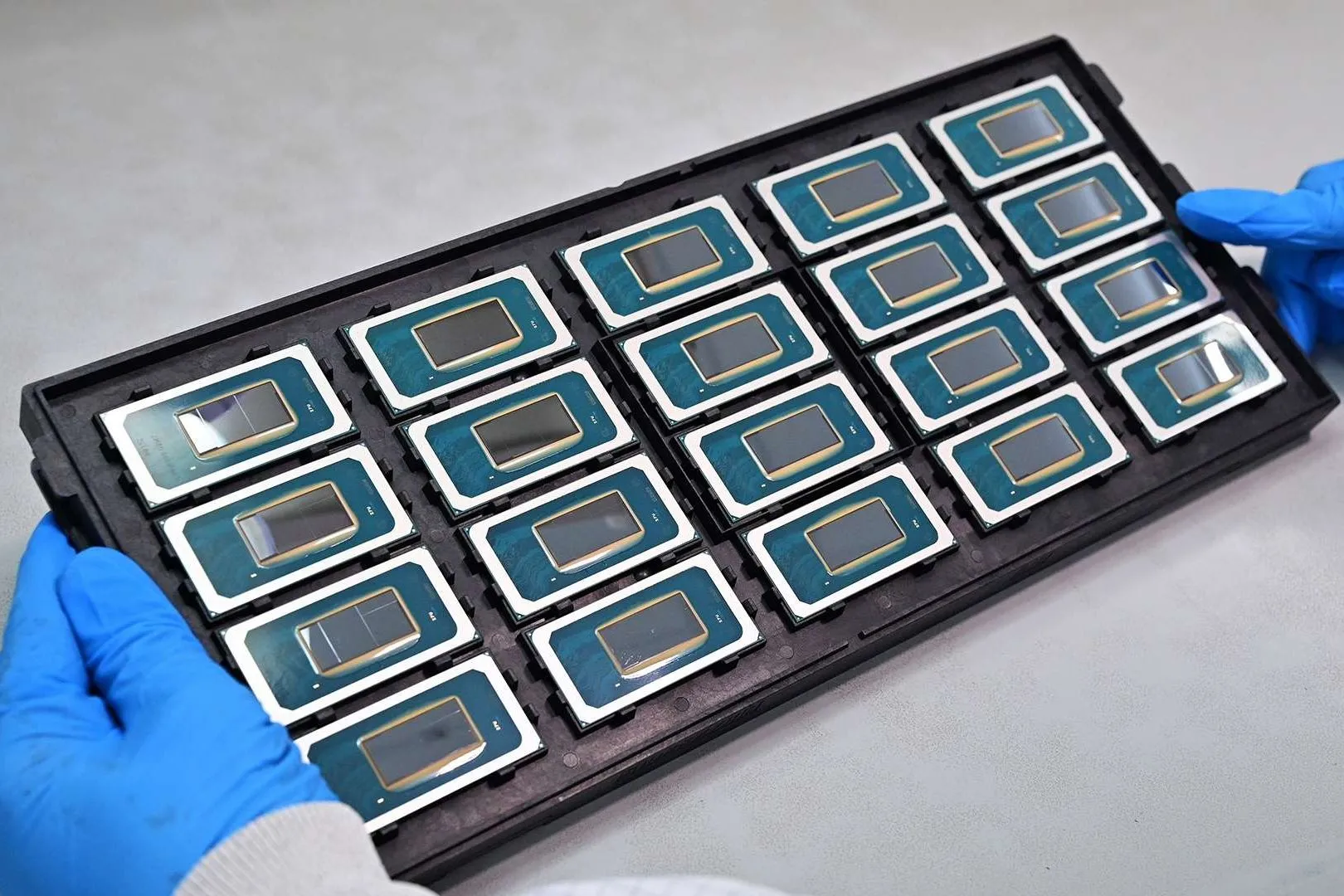

Hình ảnh các chip CPU Intel Meteor Lake Core Ultra đang được lắp ráp, minh họa quy trình sản xuất kiến trúc chiplet của Intel Foveros

Hình ảnh các chip CPU Intel Meteor Lake Core Ultra đang được lắp ráp, minh họa quy trình sản xuất kiến trúc chiplet của Intel Foveros

Vậy tại sao độ trễ thấp lại quan trọng trong trường hợp này? Độ trễ cao hơn có thể dẫn đến thời gian phản hồi chậm hơn trong các ứng dụng, hiệu suất chơi game thấp hơn, giảm khung hình quan trọng và giảm hiệu quả trong các tác vụ yêu cầu truy cập dữ liệu nhanh chóng và chính xác. Độ trễ cao hơn đồng nghĩa với hiệu suất thấp hơn, và trong một thế giới mà sức mạnh xử lý là yếu tố cốt lõi, việc giảm độ trễ là một thành phần quan trọng khi xem xét hiệu suất tính toán thô và hiệu quả tổng thể.

Ảnh hưởng của những độ trễ kết nối này được cảm nhận rõ nhất trong các tác vụ có nhiều giao tiếp xuyên chiplet, chẳng hạn như tính toán tài chính có độ trễ thấp hoặc một số ứng dụng giao dịch tần suất cao, nơi nanosecond cũng có giá trị. Công nghệ xếp chồng Foveros của Intel nhằm mục đích giảm thiểu những đánh đổi này bằng các kết nối TSV (through-silicon via) trực tiếp giữa các die. Tuy nhiên, nó cũng đối mặt với những thách thức kỹ thuật riêng, như mật độ nhiệt tăng cao và độ phức tạp trong sản xuất làm giảm năng suất.

Hiệu Quả Năng Lượng Và Hiệu Suất Gaming: Những Đánh Đổi Quan Trọng

Sau đó là vấn đề hiệu quả năng lượng. Một thiết kế nguyên khối được hưởng lợi từ giao tiếp trực tiếp giữa các nhân, trong khi kiến trúc chiplet phụ thuộc vào các bộ chuyển đổi (interposer), cầu nối (bridges) hoặc công nghệ đóng gói tiên tiến để giữ các thành phần giao tiếp với nhau. Điều này tạo ra các chi phí phụ (overheads), cả về điện năng tiêu thụ lẫn diện tích die. Những sự không hiệu quả này khó có thể biện minh cho các môi trường giới hạn điện năng như laptop, nơi mỗi miliwatt đều quý giá. Không phải ngẫu nhiên mà Intel vẫn giữ các die nguyên khối cho những dòng chip di động hiệu suất cao nhất của mình, trong khi áp dụng chiplet cho máy tính để bàn và máy chủ.

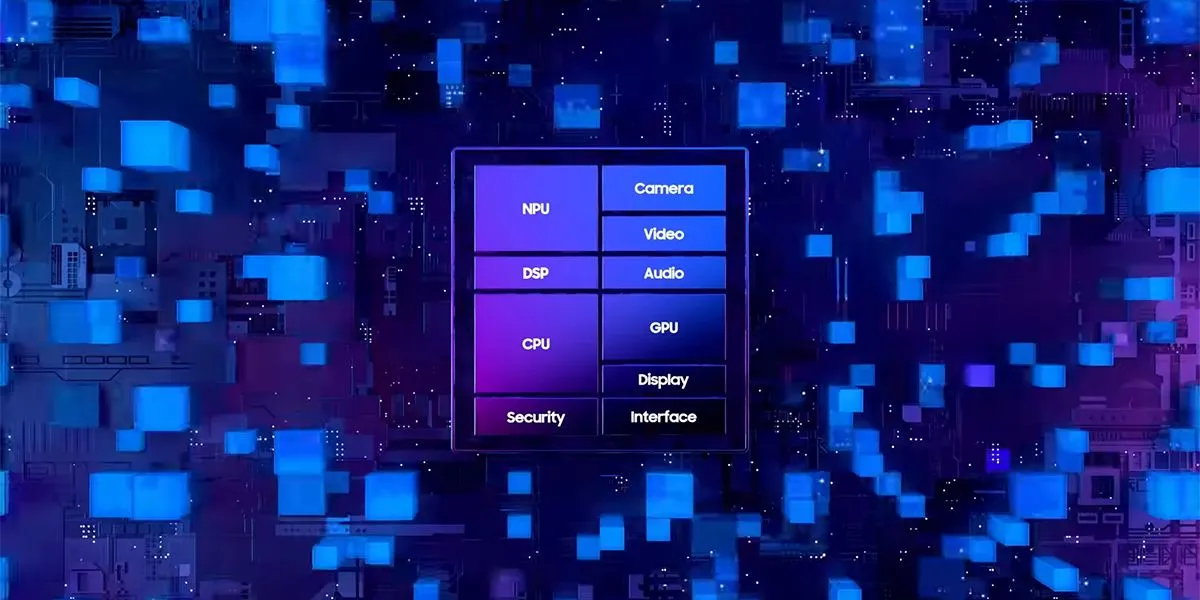

Sơ đồ kiến trúc bộ xử lý Samsung Exynos 992, thể hiện các thành phần chip được phân tách và kết nối

Sơ đồ kiến trúc bộ xử lý Samsung Exynos 992, thể hiện các thành phần chip được phân tách và kết nối

Sự gia tăng nhẹ về mức tiêu thụ điện năng do các liên kết kết nối bổ sung cũng đồng nghĩa với việc hiệu quả mở rộng công suất (power scaling efficiency) trở nên kém hơn ở mức độ sử dụng thấp. Điều này có nghĩa là thiết kế chiplet ít phù hợp hơn cho các tác vụ không sử dụng hết tất cả các nhân có sẵn. Điều này có một số tác động nhỏ đến các trường hợp sử dụng như phát lại đa phương tiện, duyệt web hoặc các tác vụ năng suất nhẹ, nơi đánh đổi hiệu quả năng lượng có thể quan trọng ngang với hiệu suất đỉnh.

Hiệu suất chơi game cũng là một “nạn nhân”. Mặc dù các bộ xử lý AMD Ryzen 3D V-Cache, chẳng hạn như Ryzen 9 9950X3D mới nhất, đã chứng minh cách chiplet có thể được tinh chỉnh cho các tác vụ cụ thể, nhưng chi phí giao tiếp xuyên chiplet (cross-chiplet communication overheads) vẫn dẫn đến thời gian khung hình biến động (variable frame times) và độ nhạy ứng dụng với độ trễ. Ví dụ, dòng Ryzen 7000 đã cải thiện những vấn đề này, nhưng vấn đề cốt lõi vẫn còn tồn tại. Có lý do tại sao một số trò chơi vẫn ưu tiên kiến trúc Raptor Lake nguyên khối của Intel hơn các triển khai Zen 4 và Zen 5 dựa trên CCD của AMD. Dù vậy, AMD đã thu hẹp một số khoảng cách hiệu suất trong hầu hết các tác vụ.

Vấn đề không chỉ là độ trễ thô, mà còn là tính cục bộ của bộ nhớ đệm (cache locality) và các kiểu truy cập bộ nhớ (memory access patterns). Khi một luồng game chạy trên một CCD nhưng cần dữ liệu trong bộ nhớ đệm L3 ở một CCD khác, nó phải đi qua Infinity Fabric, điều này tạo ra một độ trễ đáng kể. Các nhà phát triển game đã phải tối ưu code để xử lý những vấn đề này, nhưng không phải tất cả các trò chơi đều được hưởng lợi từ các tối ưu hóa đó. Đó là lý do tại sao, bất chấp những tiến bộ của AMD, một số trò chơi vẫn ưu tiên các triển khai nguyên khối tích hợp cao của Intel.

Sự Phức Tạp Trong Thiết Kế Và Sản Xuất Chiplet

Thách Thức Sản Xuất Nhưng Tiết Kiệm Chi Phí Tổng Thể

Thiết kế chiplet cũng tạo ra những thách thức về hậu cần trong sản xuất và kiểm định. Mỗi chiplet phải được kiểm tra riêng lẻ trước khi được đóng gói trong một gói cuối cùng, bổ sung thêm các bước vào quy trình sản xuất.

Điều này làm cho việc gỡ lỗi và kiểm soát chất lượng trở nên khó khăn hơn, vì một lỗi nhỏ ở một chiplet có thể làm hỏng toàn bộ gói đa die. Vấn đề tản nhiệt cũng là một mối quan ngại khi các chiplet được phân tán trên một đế nền (substrate) thay vì trên một die silicon duy nhất. Việc tản nhiệt phải được kiểm soát cẩn thận để ngăn chặn các điểm nóng (hotspots), và nhu cầu về cấp nguồn bổ sung cùng định tuyến tín hiệu cũng bổ sung thêm các ràng buộc đối với thiết kế bo mạch chủ và hệ thống làm mát.

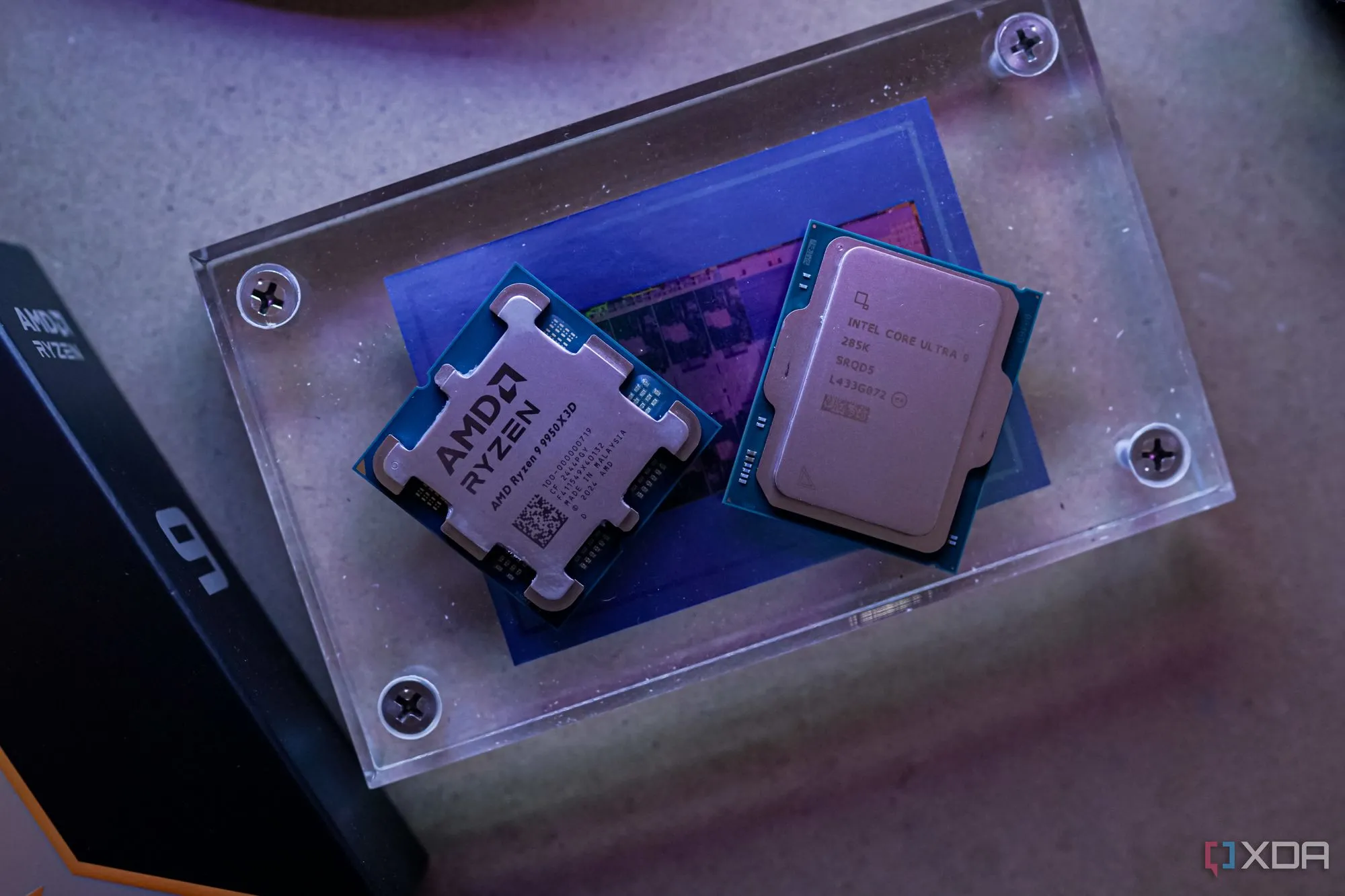

So sánh trực quan giữa CPU AMD Ryzen 9 9950X3D (thiết kế chiplet) và Intel Core Ultra 9 285K (thiết kế nguyên khối/hybrid)

So sánh trực quan giữa CPU AMD Ryzen 9 9950X3D (thiết kế chiplet) và Intel Core Ultra 9 285K (thiết kế nguyên khối/hybrid)

Tất cả những điều này không có nghĩa là chiplet là một điều tồi tệ. Chúng là một giải pháp cần thiết trong bối cảnh Định luật Moore đang dần chững lại, và kinh tế sản xuất tấm bán dẫn đòi hỏi phải tối đa hóa năng suất bằng mọi giá. Ngành công nghiệp đã tiến xa hơn việc chỉ đóng gói nhiều bóng bán dẫn hơn lên một die duy nhất, thay vào đó là chia nhỏ các thiết kế và ghép nối chúng lại bằng các kết nối tốc độ cao. Nhưng lần tới khi một công ty chip tuyên bố rằng họ đã “giải quyết” vấn đề độ trễ kết nối, hãy nhớ rằng các định luật vật lý không làm công việc PR. Ngành công nghiệp đã phần nào hy sinh một số hiệu suất để đổi lấy chi phí sản xuất thấp hơn, và thỏa thuận đó sẽ không sớm biến mất.

Tương Lai Của Chiplet: Cải Tiến Không Ngừng, Nhưng Chưa Hoàn Hảo

Việc các nhà sản xuất chip lựa chọn thiết kế dựa trên chiplet hiện đã trở thành tiêu chuẩn của ngành, nhưng chúng đi kèm với những hạn chế. Trong khi các nhà sản xuất tiếp tục tinh chỉnh các kết nối (interconnect) hay “những con đường” nối các chiplet để giảm độ trễ tổng thể và những bất hiệu quả liên quan trong thiết kế, thì những đánh đổi cơ bản về phân mảnh, chi phí điện năng và sự phức tạp phần mềm không phải là điều sẽ biến mất chỉ sau một đêm. Tương lai của các bộ xử lý dựa trên chiplet phụ thuộc vào việc giải quyết những thách thức này. Tuy nhiên, chừng nào việc tiết kiệm chi phí vẫn là động lực chính cho các lựa chọn thiết kế, thì giấc mơ về một giải pháp nguyên khối thực sự liền mạch sẽ không thúc đẩy ranh giới theo cách mà bạn có thể nghĩ.

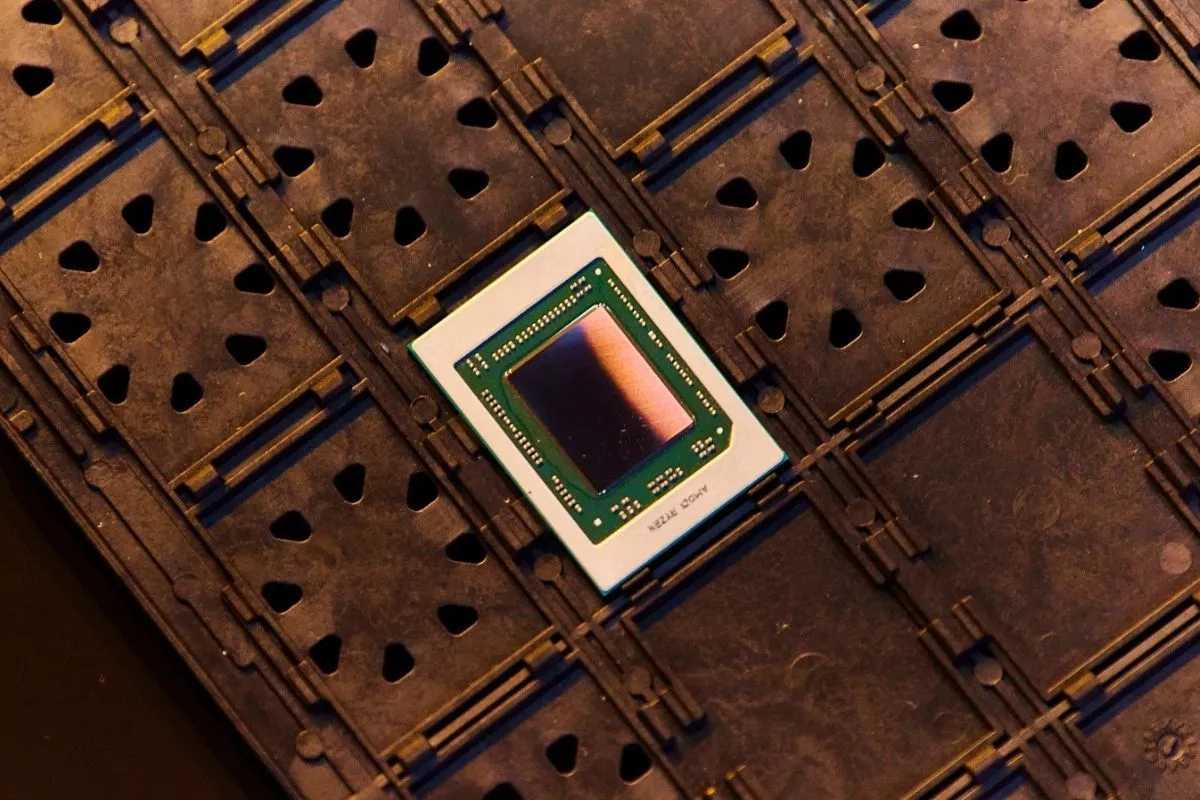

Hình ảnh các bộ xử lý AMD Ryzen 6000 series, minh họa các sản phẩm ứng dụng công nghệ chiplet

Hình ảnh các bộ xử lý AMD Ryzen 6000 series, minh họa các sản phẩm ứng dụng công nghệ chiplet

Hãy hình dung các kết nối liên chip như những đường ống, và những đường ống này trong các quy trình cần được tối ưu hóa. Việc đóng gói nhiều nhân hơn là tốt cho hiệu suất, nhưng các yếu tố như độ trễ, hiệu quả năng lượng và chi phí đều là những yếu tố cần xem xét. Các kết nối liên chip đang dần được cải thiện, nhưng để giải quyết triệt để các vấn đề cố hữu, những “lối đi” này cần được tinh chỉnh thêm. Và nhiệm vụ của các đội ngũ kỹ sư thiết kế là khắc phục những bất hiệu quả này để đẩy các thiết kế dựa trên chiplet đạt được hiệu quả tương đương với thiết kế nguyên khối, từ đó những lợi ích mà các nhà sản xuất đang hướng tới như chi phí thấp hơn và năng suất cao hơn có thể được chia sẻ thông qua hiệu suất tốt hơn đến tay người tiêu dùng.

Tóm lại, kiến trúc chiplet đại diện cho một bước tiến quan trọng trong ngành công nghiệp bán dẫn, giải quyết những thách thức về kinh tế và vật lý trong việc sản xuất chip hiệu suất cao. Tuy nhiên, con đường này không hề bằng phẳng mà ẩn chứa nhiều đánh đổi về độ trễ, hiệu quả năng lượng và sự phức tạp trong thiết kế. Mặc dù các nhà sản xuất đang không ngừng cải tiến công nghệ kết nối, những vấn đề cốt lõi vẫn còn đó. Tương lai của chiplet sẽ phụ thuộc vào khả năng của ngành công nghiệp trong việc vượt qua những rào cản này, hướng tới việc mang lại hiệu suất tối ưu và trải nghiệm người dùng vượt trội.

Hãy theo dõi 123thuthuat.com để cập nhật những phân tích sâu sắc nhất về công nghệ chiplet và các xu hướng công nghệ khác!